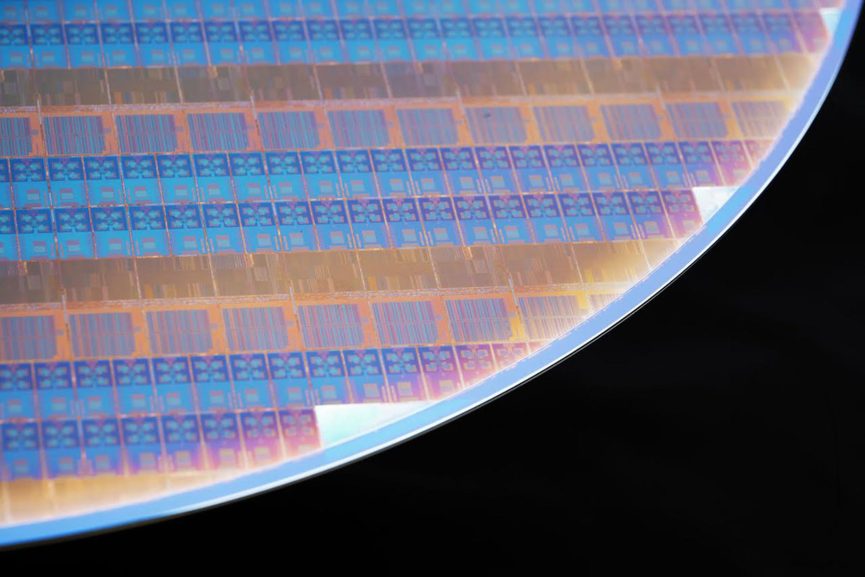

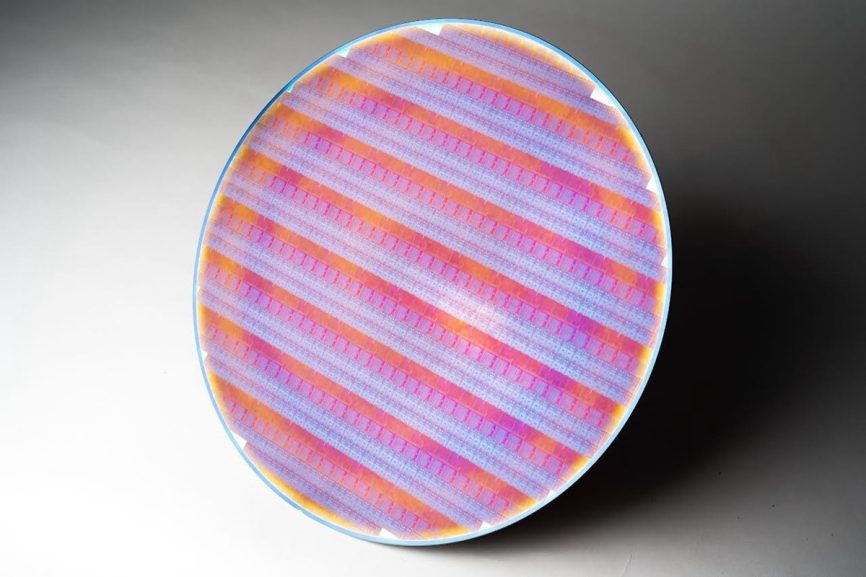

Intel 將在 6 月 11 日起於日本京都的 VLSI 大會展示 PowerVia 晶圓背面供電技術,並進一步透過兩篇論文介紹 PowerVia ,也是目前第一家實作晶圓背部供電的公司;借助將電源迴路轉移至京元背面解決訊號相互干擾問題,成為提升晶片互連的關鍵新技術, PowerVia 更使得單元利用率超過 90% ,進一步提升效能與效率; Intel 預計於 2024 年的 Intel 20A 製程後導入 PowerVia ,並與 RibbonFET 環繞式閘極技術同時成為 20A 製程以及下一代 18A 製程的一部分。

PowerVia 的概念是打破現行晶圓將包括供電、訊號的佈線全部位於單一平面的想法,借助將供電的走線全部轉移到晶圓的背面,使正面盡可能只保留訊號走線,降低兩種不同特性的訊號之間的相互干擾,也能解決訊號走線的複雜度。

▲ PowerVia 將會與 RibbonFET 成為 20A 與 18A 製程的基石,但為了加速實現技術在開發過程兩者相互脫鉤

為了進一步發揮新一代製程技術與架構的優勢與解決各式挑戰,尤其 PowerVia 將會對散熱與除錯設計產生全新挑戰, Intel 將 PowerVia 與 RibbonFET 開發脫鉤,使 Intel 能更迅速解決相干挑戰;藉由於現有製程進行驗證, Intel 團隊以開發出避免散熱問題的緩和技術,同時除錯小組也因應新架構開發全新的除錯技術,確保新架構能正確除錯,而實作測試反應穩定的良率與可靠指標,在與 RibbonFET 架構整合前即展示 PowerVia 的高度價值。

Intel 在實證中結合 EUV 極紫外光微影設計規則,在最終結果於晶片大面積實現 90% 的標準單元利用率,使單元密度提升並降低成本,同時也使平台電壓下降幅度改善超過 30% ,同時還使時脈可提高 6% ;另外 Intel 還將於 VLSI 期間公布第三篇由 Intel 技術專家 Mauro Kobrinsky 撰寫的論文,解釋 Intel 於 PowerVia 方法的研究,如在京元正面或是背面同時實現訊號與電源傳輸。

暂无评论内容